Η روزنامه اقتصادی تایوان او ادعا می کند که TSMC به یک کشف داخلی مهم برای دفع نهایی خود دست یافت تکنولوژی لیتوگرافی 2 نانومتری.

Σبه گفته این نشریه، این نقطه عطف به TSMC اجازه می دهد نسبت به اجرای تولید اولیه "ریسک تولید" 2 نانومتر در سال 2023 خوشبین است..

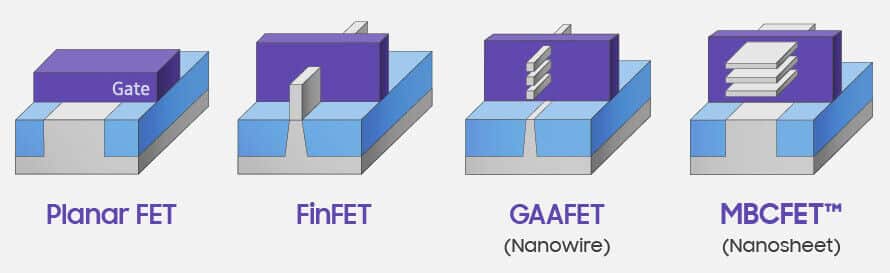

هنوز هم گزارشات قابل توجهی هستند که TSMC فناوری FinFet را برای یک ترانزیستور جلوه میدان کانال چند پل جدید (MBCFET) کنار میگذارد. مبتنی بر فناوری Gate-All-Around (GAA). این کشف مهم در راه است یک سال پس از ایجاد یک تیم داخلی توسط TSMC که هدف آن هموار کردن راه برای توسعه لیتوگرافی 2 نانومتری بود.

فناوری MBCFET معماری GAAFET را با گرفتن ترانزیستور اثر میدانی نانوسیم و "گسترش" آن برای تبدیل شدن به یک نانوصفحه گسترش میدهد. ایده اصلی این است که ترانزیستور اثر میدانی را سه بعدی کنیم.

این ترانزیستور نیمه هادی اکسید فلزی مکمل جدید می تواند کنترل مدار را بهبود بخشد و نشت جریان را کاهش دهد. این فلسفه طراحی منحصر به فرد نیست TSMC - سامسونگ قصد دارد تنوعی از این طرح را در فناوری لیتوگرافی خود توسعه دهد 3 نانومتر.

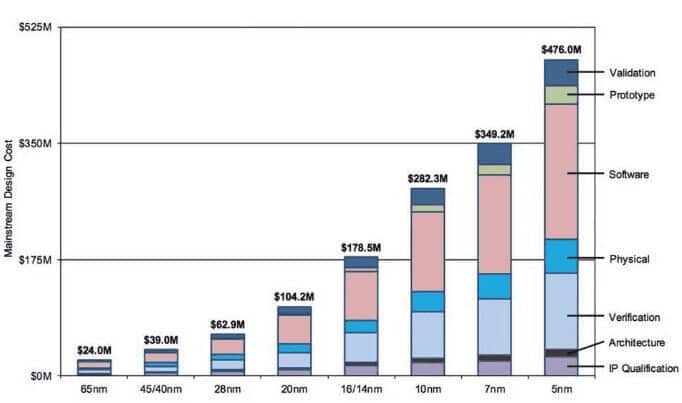

مثل همیشه، کاهش بیشتر در مقیاس تولید تراشه هزینه زیادی دارد. به ویژه، هزینه توسعه لیتوگرافی 5 نانومتری در حال حاضر به 476 میلیون دلار رسیده است، در حالی که سامسونگ بیان می کند که این فناوری GAA 3 نانومتر بیش از 500 میلیون دلار هزینه خواهد داشت. البته توسعه لیتوگرافی 2 نانومتر، از این مقادیر فراتر خواهد رفت…

فراموش نکنید که آن را دنبال کنید Xiaomi-miui.gr در اخبار گوگل تا بلافاصله در مورد تمام مقالات جدید ما مطلع شوید!

فراموش نکنید که آن را دنبال کنید Xiaomi-miui.gr در اخبار گوگل تا بلافاصله در مورد تمام مقالات جدید ما مطلع شوید!